# MRF24J40 Data Sheet

IEEE 802.15.4<sup>TM</sup> 2.4 GHz RF Transceiver

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY. PERFORMANCE. MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Migratable Memory, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Linear Active Thermistor, Mindi, MiWi, MPASM, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2006, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona, Gresham, Oregon and Mountain View, California. The Company's quality system processes and procedures are for its PIC® 8-bit MCUs, KEELOO® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# IEEE 802.15.4TM 2.4 GHz RF Transceiver

#### **Devices Included:**

MRF24J40

#### Features:

- Complete IEEE 802.15.4 Specification Compliant

- Supports MiWi™, ZigBee™ and Proprietary Protocols

- Simple, 4-Wire SPI Interface

- Integrated 20 MHz and 32.768 kHz Oscillator Drive

- 20 MHz Reference Clock Output:

- Available to drive microcontroller oscillator

- · Supports Power-Saving mode

- Low-Current Consumption, Typical 18 mA in RX mode and 22 mA in TX mode

- Typical 2 μA Sleep mode

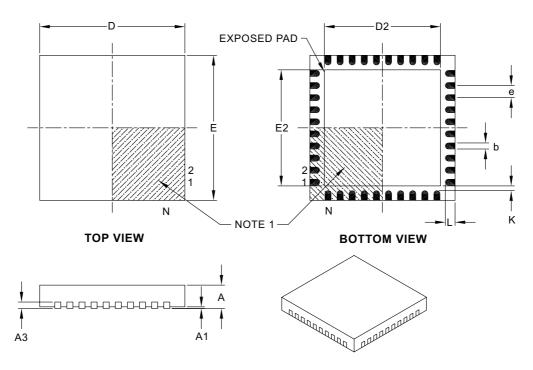

- Small, 40-Pin Leadless QFN 6x6 mm<sup>2</sup> Package

#### **RF/Analog Features:**

- ISM Band 2.405-2.48 GHz Operation

- -91 dBm Typical Sensitivity and +5 dBm Maximum Input Level

- +0 dBm Typical Output Power and 38.75 dB TX Power Control Range

- Differential RF Input/Output and Integrated TX/RX Switch

- Integrated Low Phase Noise VCO, Frequency Synthesizer and PLL Loop Filter

- · Digital VCO and Filter Calibration

- Integrated RSSI ADC and I/Q DACs

- · Integrated LDO

- · High Receiver and RSSI Dynamic Range

#### **MAC/Baseband Features:**

- Hardware CSMA-CA Mechanism, Automatic ACK Response and FCS Check

- Independent Beacon, Transmit and GTS FIFO

- Hardware Security Engine (AES-128) with CTR, CCM and CBC-MAC modes

- Supports all CCA modes and RSS/LQI

- Automatic Packet Retransmit Capability

- Supports In-Line or Stand-Alone modes for both Encryption and Decryption

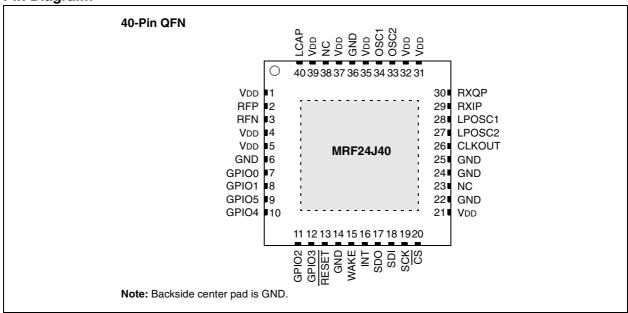

### Pin Diagram:

#### **Table of Contents**

| 1.0   | Overview                                         | 3    |

|-------|--------------------------------------------------|------|

| 2.0   | External Connections                             | 7    |

| 3.0   | Memory Organization                              | 9    |

| 4.0   | Serial Peripheral Interface (SPI)                | . 13 |

| 5.0   | IEEE 802.15.4™-2003                              | . 19 |

| 6.0   | Initialization                                   |      |

| 7.0   | Transmitting and Receiving Packets               | . 29 |

| 8.0   | Interrupts                                       | . 35 |

| 9.0   | General Purpose I/O                              | . 39 |

| 10.0  | Electrical Characteristics                       |      |

| 11.0  | Packaging Information                            | . 45 |

| Appe  | ndix A: Layout and Part Selection                | . 47 |

| Appe  | ndix B: MRF24J40 Schematic and Bill of Materials | . 55 |

|       |                                                  |      |

| The I | /icrochip Web Site                               | . 61 |

| Custo | omer Change Notification Service                 | . 61 |

| Custo | omer Support                                     | . 61 |

| Read  | er Response                                      | . 62 |

|       | uct Identification System                        | 63   |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

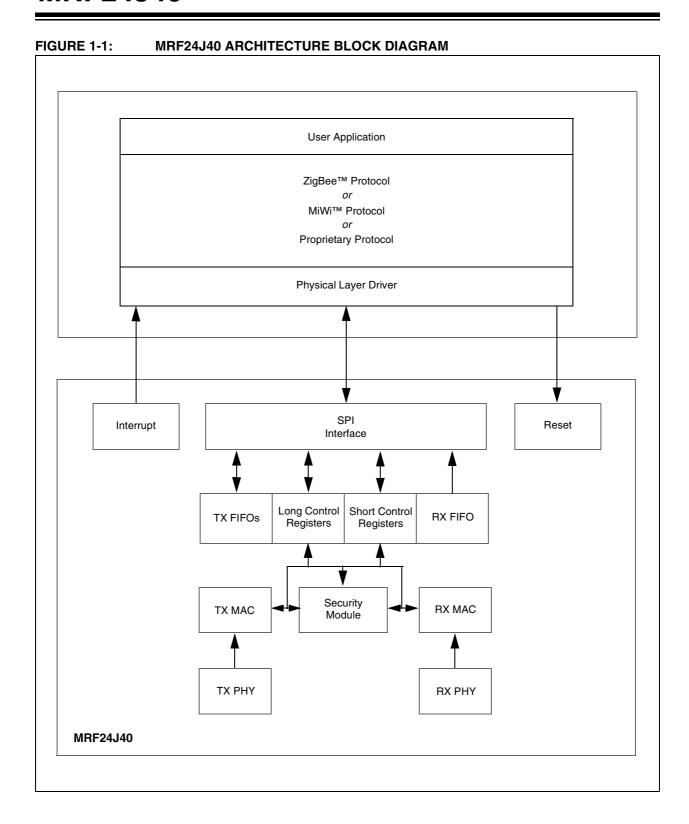

### 1.0 OVERVIEW

The MRF24J40 is an IEEE 802.15.4-2003 compliant transceiver supporting MiWi™, ZigBee™ and other proprietary protocols. The MRF24J40 integrates wireless RF, PHY layer baseband and MAC layer architectures that can be combined with a simple microprocessor to apply low data rate to a multitude of applications that include home automation, consumer electronics, PC peripherals, toys, industrial automation and more. The MRF24J40 device integrates a receiver, transmitter, VCO and PLL into a single integrated circuit. It uses advanced radio architecture to minimize external part count and power consumption. The MRF24J40 MAC/baseband provides hardware architecture for both IEEE 802.15.4 MAC and PHY layers. It mainly consists of TX/RX FIFOs, a CSMA-CA controller, superframe constructor, receive frame filter, security engine and digital signal processing module. The MRF24J40 is fabricated by advanced 0.18 µm CMOS process and is offered in a 40-pin QFN 6x6 mm<sup>2</sup> package.

Features are summarized in Table 1-1 and the pinout for this device is listed in Table 1-2.

The MRF24J40 consists of four major functional blocks:

- An SPI interface that serves as a communication channel between the host controller and the MRF24J40.

- Control registers which are used to control and monitor the MRF24J40.

- 3. The MAC (Medium Access Control) module that implements IEEE 802.3™ compliant MAC logic.

- 4. The PHY (Physical Layer) driver that encodes and decodes the analog data.

The device also contains other support blocks, such as the on-chip voltage regulator, security module and system control logic.

TABLE 1-1: DEVICE FEATURES FOR THE MRF24J40 (40-PIN DEVICE)

| Features                               | MRF24J40                                |

|----------------------------------------|-----------------------------------------|

| IEEE 802.15.4™ Specification Compliant | Yes                                     |

| Integrated Oscillator Drive            | 20 MHz and 32.768 kHz                   |

| Reference Clock Output                 | 20 MHz                                  |

| Power-Saving Mode Support              | Yes                                     |

| Current Consumption                    | Typical 18 mA in RX and 22 mA in TX     |

| Sleep Mode                             | 2 μA Typical                            |

| Serial Communications                  | SPI (4-wire)                            |

| Packages                               | 40-Pin Leadless QFN 6x6 mm <sup>2</sup> |

**Advance Information**

## 1.1 Pin Descriptions

TABLE 1-2: MRF24J40 PIN DESCRIPTIONS

| Pin | Symbol | Туре   | Description                                                                                           |

|-----|--------|--------|-------------------------------------------------------------------------------------------------------|

| 1   | VDD    | Power  | RF power supply. Bypass with a capacitor as close to the pin as possible.                             |

| 2   | RFP    | AIO    | Differential RF input/output (+).                                                                     |

| 3   | RFN    | AIO    | Differential RF input/output (-).                                                                     |

| 4   | VDD    | Power  | RF power supply. Bypass with a capacitor as close to the pin as possible.                             |

| 5   | VDD    | Power  | Guard ring power supply. Bypass with a capacitor as close to the pin as possible.                     |

| 6   | GND    | Ground | Guard ring ground.                                                                                    |

| 7   | GPIO0  | DIO    | General purpose digital I/O, also used as external PA enable.                                         |

| 8   | GPIO1  | DIO    | General purpose digital I/O, also used as external TX/RX switch control.                              |

| 9   | GPIO5  | DIO    | General purpose digital I/O.                                                                          |

| 10  | GPIO4  | DIO    | General purpose digital I/O.                                                                          |

| 11  | GPIO2  | DIO    | General purpose digital I/O, also used as external TX/RX switch control.                              |

| 12  | GPIO3  | DIO    | General purpose digital I/O.                                                                          |

| 13  | RESET  | DI     | Global hardware Reset pin active-low.                                                                 |

| 14  | GND    | Ground | Ground for digital circuit.                                                                           |

| 15  | WAKE   | DI     | External wake-up trigger.                                                                             |

| 16  | INT    | DO     | Interrupt pin to microcontroller.                                                                     |

| 17  | SDO    | DIO    | Serial interface data output from MRF24J40.                                                           |

| 18  | SDI    | DIO    | Serial interface data input to MRF24J40.                                                              |

| 19  | SCK    | DI     | Serial interface clock.                                                                               |

| 20  | CS     | DI     | Serial interface enable.                                                                              |

| 21  | VDD    | Power  | Digital circuit power supply. Bypass with a capacitor as close to the pin as possible.                |

| 22  | GND    | Ground | Ground for digital circuit.                                                                           |

| 23  | NC     | _      | No Connection, do not connect anything to this pin.                                                   |

| 24  | GND    | Ground | Ground for digital circuit.                                                                           |

| 25  | GND    | Ground | Ground for digital circuit.                                                                           |

| 26  | CLKOUT | DIO    | 20/10/5/2.5 MHz clock output.                                                                         |

| 27  | LPOSC2 | Al     | 32 kHz crystal input (-).                                                                             |

| 28  | LPOSC1 | Al     | 32 kHz crystal input (+).                                                                             |

| 29  | RXIP   | AO     | Analog RX I channel output (+).                                                                       |

| 30  | RXQP   | AO     | Analog RX Q channel output (+).                                                                       |

| 31  | VDD    | Power  | Power supply for band gap reference circuit. Bypass with a capacitor as close to the pin as possible. |

| 32  | VDD    | Power  | Power supply for analog circuit. Bypass with a capacitor as close to the pin as possible.             |

| 33  | OSC2   | Al     | 20 MHz crystal input (-).                                                                             |

| 34  | OSC1   | Al     | 20 MHz crystal input (+).                                                                             |

| 35  | VDD    | Power  | PLL power supply. Bypass with a capacitor as close to the pin as possible.                            |

| 36  | GND    | Ground | Ground for PLL.                                                                                       |

| 37  | VDD    | Power  | Charge pump power supply. Bypass with a capacitor as close to the pin as possible.                    |

| 38  | NC     | _      | No Connection.                                                                                        |

| 39  | VDD    | Power  | VCO supply. Bypass with a capacitor as close to the pin as possible.                                  |

| 40  | LCAP   | _      | PLL loop filter external capacitor. Connected to external 180 pF capacitor.                           |

**Legend:** A = Analog, D = Digital, I = Input, O = Output

NOTES:

### 2.0 EXTERNAL CONNECTIONS

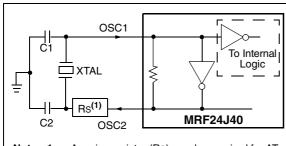

#### 2.1 Oscillator

The MRF24J40 is designed to operate at 20 MHz with a crystal connected to the OSC1 and OSC2 pins. A typical oscillator circuit is shown in Figure 2-1.

# FIGURE 2-1: CRYSTAL OSCILLATOR OPERATION

Note 1: A series resistor (Rs) may be required for AT strip cut crystals.

#### 2.2 Oscillator Start-up

The MRF24J40 PHY has an internal PLL that must lock before the device is capable of transmitting or receiving packets. After a full Power-on Reset, the device requires 2 ms to lock. During this delay, all registers and buffer memory may still be read and written to through the SPI bus. However, software should not attempt to transmit any packets (set the TXRTS (TXNMTRIG<0>)), or access any MAC or PHY registers during this period.

#### 2.3 CLKOUT Pin

The clock out pin is provided to the system designer for use as the host controller clock or as a clock source for other devices in the system. The CLKOUT has an internal prescaler which can divide the output by 1, 2, 4 or 8. The CLKOUT function is enabled via the CLKCTRL register (Register 2-1) and the prescaler is selected via the RFCTRL7 register (Register 2-2).

#### REGISTER 2-1: CLKCTRL: DIVIDED SLEEP CLOCK (50 kHz) SELECTION REGISTER

| R/W-0 | U-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 |

|-------|-----|--------|-------|-------|-------------|-------|-------|

| r     | _   | CLKOEN |       |       | SCLKDIV<4:0 | >     |       |

| bit 7 |     |        |       |       |             |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7 Reserved: Maintain as '0' bit 6 Unimplemented: Read as '0'

bit 5 CLKOEN: 20 MHz Clock Output Enable bit

1 = Disable0 = Enable

bit 4-0 SCLKDIV4:SCLKDIV0: Divided SLPCLK Selection bits

Divided by 2<sup>n</sup>.

#### REGISTER 2-2: RFCTRL7: RF CONTROL REGISTER 7

| R/W-0       | R/W-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0  |

|-------------|-------|-----|-----|-----|-----|-------|--------|

| SLPCLK<7:6> |       | _   | -   | -   | _   | CLKDI | V<1:0> |

| bit 7       |       |     |     |     |     |       | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-6 SLPCLK7:SLPCLK6: Sleep Clock Selection bits

00 = None

01 = External crystal

10 = Internal ring oscillator

11 = Reserved

bit 5-2 Unimplemented: Read as '0'

bit 1-0 CLKDIV1:CLKDIV0: MRF24J40 Clock Output Frequency bits

00 = 2.5 MHz

01 = 5 MHz

10 = **10 MHz**

11 = 20 MHz

To create a clean clock signal, the CLKOUT pin is held low for a period when power is first applied. After the Power-on Reset ends, the Oscillator Start-up Timer (OST) will begin counting. When the OST expires, the CLKOUT pin will begin outputting its default frequency of 2.5 MHz (main clock divided by 8).

### 2.4 RF Output

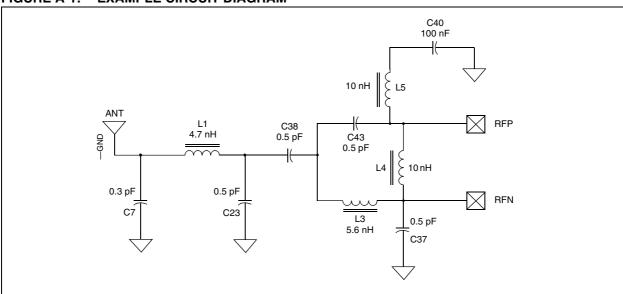

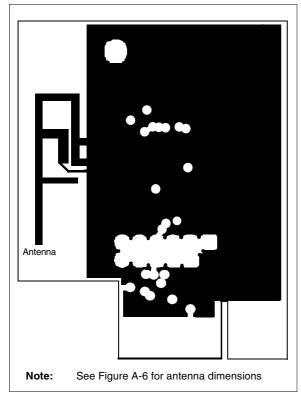

RFP and RFN are the differential RF input/output pins. These pins are connected to the antenna of the system, as seen in the example circuit diagram in Figure A-1. L5 is an RF choke. This inductor filters out non 2.4 GHz voltages. L3, L4, C37 and C43 act as a balun. The balun converts a differential unbalanced input and converts it to a balanced singled-ended output and visa versa. L1, C23 and C38 form a pi-type matching circuit to match the impedance of the balun to the impedance of the antenna. This circuit is not required if the impedance of the balun matches the antenna impedance. Refer to Appendix A.1 "Layout Considerations and RF Measurements" for more details about board layout and part selection concerning the RF output pins.

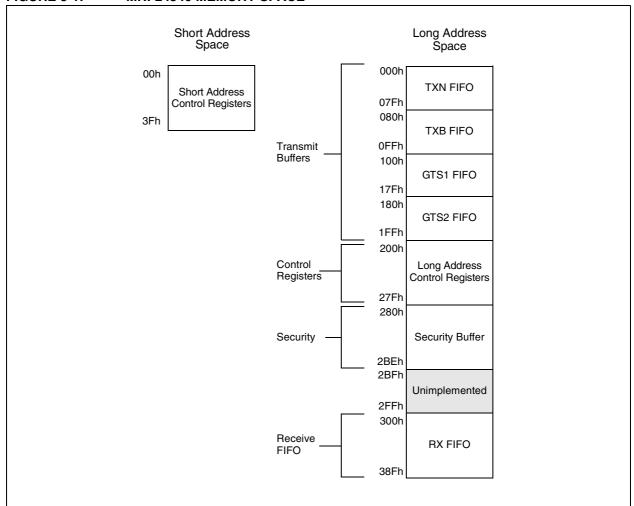

#### 3.0 MEMORY ORGANIZATION

All memory in the MRF24J40 is implemented as static RAM. There are five types of memory in the MRF24J40:

- · Short Address Control Registers

- Long Address Control Registers

- · Transmit Buffers

- · Receive Buffers

- · Security Buffer

The control registers, both long and short, are used for configuration, control, and status retrieval of the MRF24J40. The control registers are directly read and written to by the SPI interface. The transmit and receive buffers contain transmit and receive memory used by the controller to transmit and receive data.

The security buffer provides an engine for the MRF24J40 MAC, which is compatible with the IEEE 802.15.4 LR-WPAN (ZigBee). The security buffer contains the following features:

- Transmit encryption and receive decryption.

- · Seven-mode security suite.

- 64 x 8-bit security RAM for security suite storing; one receive key and three transmit keys for TX FIFOs. Beacon FIFO and GTS2 FIFO share the same key space since they will not conflict with each other. Normal FIFO and GTS1 FIFO both have their own transmit key.

- Security of APL and NWK layers can be achieved using the same engine. The upper layer security function is compliant to the ZigBee V1.0 and ZigBee 2006 specifications.

The SPI interface used to write and read these registers is described in **Section 4.0** "**Serial Peripheral Interface (SPI)**".

Figure 3-1 shows the data memory organization for the MRF24J40.

FIGURE 3-1: MRF24J40 MEMORY SPACE

## 3.1 Control Registers

The control registers provide the main interface between the host controller and the on-chip RF controller logic. Writing to these registers controls the operation of the interface, while reading the registers allows the host controller to monitor operations. The control register memory is partitioned into the short address control register section and the long address control register section.

All reserved registers may be read but their contents must not be changed. When reading and writing to registers which contain reserved bits, any rules stated in the register definition should be observed.

FIGURE 3-2: MRF24J40 SHORT ADDRESS CONTROL REGISTER MAPPING

| -   |         | , , |          | , - |      | ,   |           |

|-----|---------|-----|----------|-----|------|-----|-----------|

| 00h | RXMCR   | 10h |          | 20h | _    | 30h | _         |

| 01h | PANIDL  | 11h | _        | 21h | _    | 31h | ISRSTS    |

| 02h | PANIDH  | 12h | _        | 22h | _    | 32h | INTMSK    |

| 03h | SADRL   | 13h | _        | 23h | _    | 33h | GPIO      |

| 04h | SADRH   | 14h | -        | 24h | TXSR | 34h | TRISGPIO  |

| 05h | EADR0   | 15h | _        | 25h | _    | 35h | _         |

| 06h | EADR1   | 16h |          | 26h | _    | 36h | RFCTL     |

| 07h | EADR2   | 17h |          | 27h | _    | 37h | _         |

| 08h | EADR3   | 18h | _        | 28h | _    | 38h | -         |

| 09h | EADR4   | 19h | _        | 29h | _    | 39h | -         |

| 0Ah | EADR5   | 1Ah | _        | 2Ah | _    | 3Ah | BBREG2    |

| 0Bh | EADR6   | 1Bh | TXNMTRIG | 2Bh | _    | 3Bh | _         |

| 0Ch | EADR7   | 1Ch |          | 2Ch | _    | 3Ch | _         |

| 0Dh | RXFLUSH | 1Dh | _        | 2Dh | _    | 3Dh | _         |

| 0Eh | _       | 1Eh | _        | 2Eh | _    | 3Eh | BBREG6    |

| 0Fh | _       | 1Fh | _        | 2Fh | _    | 3Fh | RSSITHCCA |

FIGURE 3-3: MRF24J40 LONG ADDRESS CONTROL REGISTER MAPPING

| 200h | RFCTRL0 | 210h | _        | 220h | CLKCTRL | 230h | _ | 240h | _ |

|------|---------|------|----------|------|---------|------|---|------|---|

| 201h | _       | 211h | CLKINTCR | 221h | _       | 231h | _ | 241h | _ |

| 202h | RFCTRL2 | 212h | _        | 222h | _       | 232h | _ | 242h | _ |

| 203h | RFCTRL3 | 213h | _        | 223h | _       | 233h | _ | 243h | _ |

| 204h | _       | 214h | _        | 224h | _       | 234h | _ | 244h | _ |

| 205h | _       | 215h | _        | 225h | _       | 235h | _ | 245h | _ |

| 206h | RFCTRL6 | 216h | _        | 226h | _       | 236h | _ | 246h | _ |

| 207h | RFCTRL7 | 217h | _        | 227h | _       | 237h | _ | 247h | _ |

| 208h | RFCTRL8 | 218h | _        | 228h | _       | 238h | _ | 248h | _ |

| 209h | _       | 219h | _        | 229h | _       | 239h | _ | 249h | _ |

| 20Ah | _       | 21Ah | _        | 22Ah | _       | 23Ah | _ | 24Ah | _ |

| 20Bh | _       | 21Bh | _        | 22Bh | _       | 23Bh | - | 24Bh | _ |

| 20Ch | _       | 21Ch | _        | 22Ch | _       | 23Ch | _ | 24Ch | _ |

| 20Dh | _       | 21Dh | _        | 22Dh | _       | 23Dh | _ |      |   |

| 20Eh | _       | 21Eh | _        | 22Eh | _       | 23Eh | _ |      |   |

| 20Fh | _       | 21Fh | _        | 22Fh | _       | 23Fh | _ |      |   |

| L    |         | I L  |          | J L  |         | ı L  |   | 1    |   |

## 3.2 MRF24J40 Address Summary

TABLE 3-1: REGISTER FILE SHORT ADDRESS SUMMARY

| File Name | Bit 7   | Bit 6   | Bit 5      | Bit 4           | Bit 3         | Bit 2     | Bit 1     | Bit 0   | Value on<br>POR | Details on page: |

|-----------|---------|---------|------------|-----------------|---------------|-----------|-----------|---------|-----------------|------------------|

| RXMCR     | TXCRCEN | BBLPBK  | ACKEN      | MACLPBK         | PANCOORD      | COORD     | RXCRCEN   | PROMI   | 0000 0000       | 21               |

| PANIDL    |         |         | MAC        | PAN Low By      | te (PANL<7:0> | )         |           |         | 0000 0000       | 26               |

| PANIDH    |         |         | MAC        | PAN High Byte   | e (PANH<15:8  | >)        |           |         | 0000 0000       | 26               |

| SADRL     |         |         | MAC Short  | Address Low     | Byte (SADDRI  | L<7:0>)   |           |         | 0000 0000       | 27               |

| SADRH     |         |         | MAC Short  | Address High I  | Byte (SADDRI  | H<15:8>)  |           |         | 0000 0000       | 27               |

| EADR0     |         |         | L          | SB of EUI (EA   | ADR0<7:0>)    |           |           |         | 0000 0000       | 26               |

| EADR1     |         |         | Ву         | te 2 of EUI (E/ | ADR1<15:8>)   |           |           |         | 0000 0000       | 26               |

| EADR2     |         |         | Byt        | e 3 of EUI (EA  | ADR2<23:16>)  |           |           |         | 0000 0000       | 26               |

| EADR3     |         |         | Byt        | e 4 of EUI (EA  | ADR3<31:24>)  |           |           |         | 0000 0000       | 26               |

| EADR4     |         |         | Byt        | e 5 of EUI (EA  | ADR4<39:32>)  |           |           |         | 0000 0000       | 26               |

| EADR5     |         |         | Byt        | e 6 of EUI (EA  | DR5<47:40>)   |           |           |         | 0000 0000       | 26               |

| EADR6     |         |         | Byt        | e 7 of EUI (EA  | DR6<55:48>)   |           |           |         | 0000 0000       | 26               |

| EADR7     |         |         | M          | SB of EUI (EAI  | DR7<63:56>)   |           |           |         | 0000 0000       | 26               |

| RXFLUSH   | _       | r       | r          | RXWRTBLK        | CMDONLY       | DATAONLY  | BCNONLY   | RXFLUSH | -000 0000       | 34               |

| TXNMTRIG  | _       | _       | ı          | PENDACK         | INDIRECT      | ACKREQ    | SECEN     | TXRTS   | 0 0000          | 30               |

| TXSR      | TXRET   | RY<7:6> | CCAFAIL    | r               | r             | r         | r         | r       | 0000 0000       | 31               |

| ISRSTS    | SLPIF   | WAKEIF  | HSYMTMRIF  | SECIF           | RXIF          | GTS2TXIF  | GTS1TXIF  | TXIF    | 0000 0000       | 36               |

| INTMSK    | SLPMSK  | WAKEMSK | HSYMTMRMSK | SECMSK          | RXMSK         | GTS2TXMSK | GTS1TXMSK | TXMSK   | 1111 1111       | 37               |

| GPIO      | _       | _       | GPIO5      | GPIO4           | GPIO3         | GPIO2     | GPIO1     | GPIO0   | 00 0000         | 39               |

| TRISGPIO  | _       | _       | TRISGP5    | TRISGP4         | TRISGP3       | TRISGP2   | TRISGP1   | TRISGP0 | 00 0000         | 40               |

| RFCTL     | r       | _       | _          | r               | r             | RFRST     | r         | r       | 00 0000         | 24               |

| BBREG2    | CCAMO   | DE<7:6> |            | CCATHRE         | S<5:2>        |           | _         | _       | 0000 00         | 25               |

| BBREG6    | RSSIREQ | RXRSSI  | r          | r r r r RSSIRDY |               |           |           |         |                 | 25               |

| RSSITHCCA |         |         |            | RSSITHRE        | S<7:0>        |           |           |         | 0000 0000       | 23               |

**Legend:** - = unimplemented, r = reserved. Shaded cells are unimplemented, read as '0'.

TABLE 3-2: REGISTER FILE LONG ADDRESS SUMMARY

|           |       |        | 0.,       | G /\DD       |          | *** ** * * |         |           |              |                  |

|-----------|-------|--------|-----------|--------------|----------|------------|---------|-----------|--------------|------------------|

| File Name | Bit 7 | Bit 6  | Bit 5     | Bit 4        | Bit 3    | Bit 2      | Bit 1   | Bit 0     | Value on POR | Details on page: |

| RFCTRL0   |       | CHANN  | EL<7:4>   |              | _        | _          | _       | _         | 0000         | 24               |

| RFCTRL2   | RFPLL | r      | r         | r            | r        | _          | _       | _         | 0000 0       | 22               |

| RFCTRL3   |       | T      | XPOWER<7: | 3>           |          | 1          | _       | _         | 0000 0       | 22               |

| RFCTRL6   | TXFIL | _      | r         | r            | BATMONEN | _          | _       | _         | 0-00 0       | 23               |

| RFCTRL7   | SLPCL | K<7:6> | ı         | _            | _        | 1          | CLKI    | OIV<1:0>  | 0000         | 8                |

| RFCTRL8   | ı     | _      | ı         | RF_VCO       | _        | 1          | _       | SLPCLKOUT | 00           | 23               |

| CLKINTCR  | _     | _      | _         | _            | _        | _          | INTEDGE | SLPCLKEN  | 00           | 38               |

| CLKCTRL   | r     | _      | CLKOEN    | SCLKDIV<4:0> |          |            |         |           | 0-00 0000    | 7                |

$\textbf{Legend:} \qquad \text{-} = \text{unimplemented, r = reserved. Shaded cells are unimplemented, read as `0'.}$

NOTES:

# 4.0 SERIAL PERIPHERAL INTERFACE (SPI)

#### 4.1 Overview

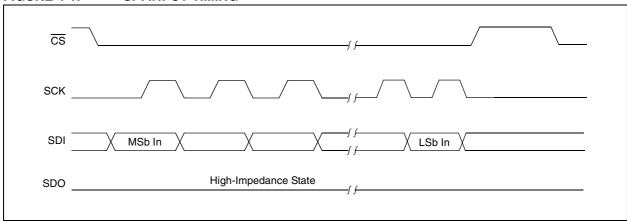

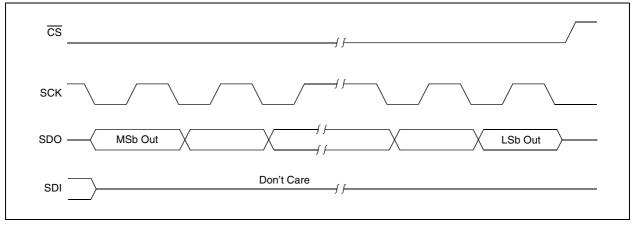

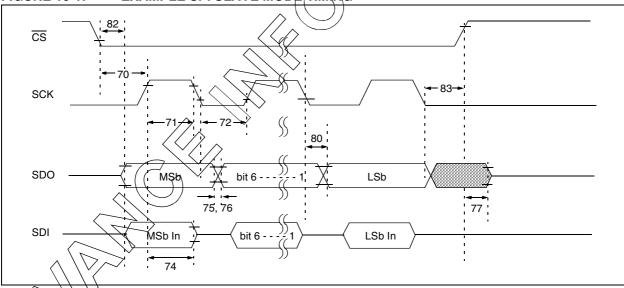

The MRF24J40 is designed to interface directly with the Serial Peripheral Interface (SPI) port available on many microcontrollers. The implementation used on this device supports SPI mode 0,0 only. In addition, the SPI port requires that SCK be Idle in a low state; selectable clock polarity is not supported.

Commands and data are sent to the device via the SDI pin, with data being clocked in on the rising edge of SCK. Data is driven out by the MRF24J40 on the SDO line, on the falling edge of SCK. The  $\overline{\text{CS}}$  pin must be held low while any operation is performed and returned high when finished.

The MRF24J40 accesses the short and long RAM banks in a slightly different manner. The following sections describe the required waveforms in order to read and write from both short and long RAM addresses.

FIGURE 4-1: SPI INPUT TIMING

FIGURE 4-2: SPI OUTPUT TIMING

## 4.2 Short Address Register Interface

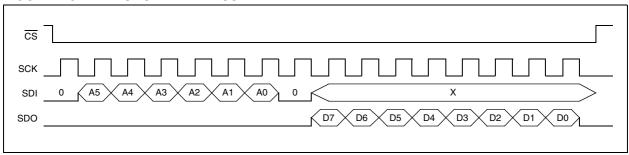

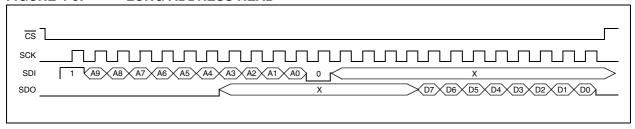

# 4.2.1 READING SHORT ADDRESS REGISTERS

The short address space is accessed by sending a 'o' as the first bit of the SPI transfer. The following 6 bits are the address of the target register. The final bit of the first byte is a 'o' to indicate that the command is a read. On the next clock edge of SCK, the Most Significant bit of the register will shift out, followed by the rest of the bits.

#### FIGURE 4-3: SHORT ADDRESS READ

#### **EXAMPLE 4-1: SHORT ADDRESS READ EXAMPLE**

```

BYTE GetShortRAMAddress(BYTE address)

{

BYTE toReturn;

CSn = 0;

SPIPut((address<<1)&0b01111110);

toReturn = SPIGet();

CSn = 1;

return toReturn;

}</pre>

```

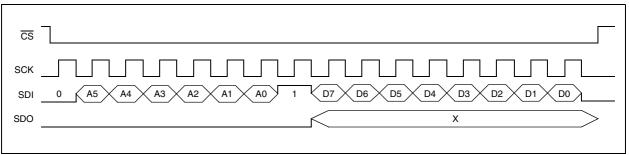

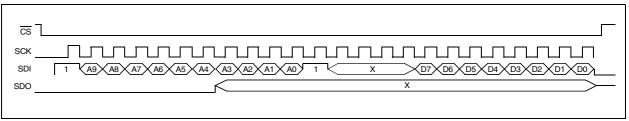

# 4.2.2 WRITING SHORT ADDRESS REGISTERS

The short address space is accessed by sending a '0' as the first bit of the SPI transfer. The following 6 bits are the address of the target register. The final bit of the first byte is a '1' to indicate that the command is a write. On the next clock edge of SCK, the Most Significant bit of the register will shift out, followed by the rest of the bits.

#### FIGURE 4-4: SHORT ADDRESS WRITE

#### **EXAMPLE 4-2:** SHORT ADDRESS WRITE EXAMPLE

```

void SetShortRAMAddress(BYTE address, BYTE value)

{

CSn = 0;

SPIPut(((address<<1)&0b01111111)|0x01);

SPIPut(value);

CSn = 1;

}</pre>

```

## 4.3 Long Address Register Interface

# 4.3.1 READING LONG ADDRESS REGISTERS

The long address space is accessed by sending a '1' as the first bit of the SPI transfer. The following 10 bits are the address of the target register. The final bit is a '0' to indicate that the command is a read. On the next clock edge of SCK, the Most Significant bit of the register will shift out, followed by the rest of the bits.

#### FIGURE 4-5: LONG ADDRESS READ

### **EXAMPLE 4-3: LONG ADDRESS READ EXAMPLE**

```

BYTE GetLongRAMAddress(WORD address)

{

BYTE toReturn;

CSn = 0;

SPIPut(((address>>3)&0b01111111) | 0x80);

SPIPut(((address<<5)&0b11100000));

toReturn = SPIGet();

CSn = 1;

return toReturn;

}</pre>

```

# 4.3.2 WRITING LONG ADDRESS REGISTERS

The long address space is accessed by sending a '1 ' as the first bit of the SPI transfer. The following 10 bits are the address of the target register. The final bit is a '1 ' to indicate that the command is a write. On the next clock edge of SCK, the Most Significant bit of the register will shift out, followed by the rest of the bits.

#### 4.4 Buffer Interface

The receive and transmit buffers in the MRF24J40 are located in the long RAM address space. These buffers are accessed using the same process as accessing the long RAM control addresses. The received buffer is read-only and should not be written to. The use of these buffers is described in **Section 7.0** "**Transmitting and Receiving Packets**".

#### FIGURE 4-6: LONG ADDRESS WRITE

#### **EXAMPLE 4-4: LONG ADDRESS WRITE EXAMPLE**

NOTES:

### 5.0 IEEE 802.15.4<sup>™</sup>-2003

#### 5.1 Overview

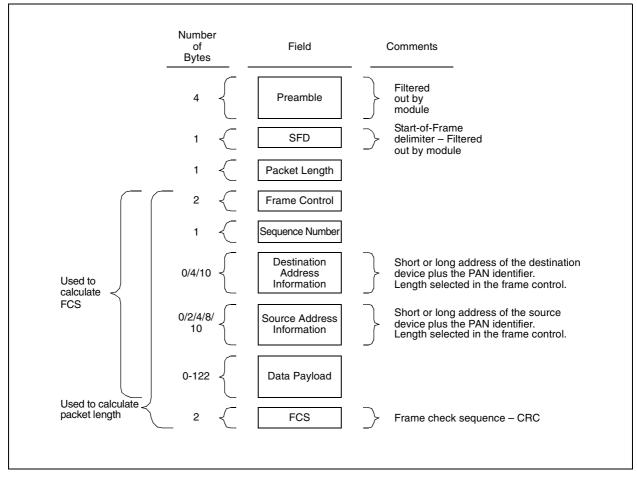

Before discussing the use of the MRF24J40, it may be helpful to review the structure of a typical data frame. Users requiring more information should refer to the IEEE 802.15.4 Standard.

#### 5.2 Packet Format

Normal IEEE 802.15.4 compliant packets are between 5 and 127 bytes long. They are made up of several possible fields: destination address information, source address information, a length field, data payload and a Cyclic Redundancy Check (CRC). Additionally, a 4-byte preamble field and Start-of-Frame Delimiter (SFD) byte are appended to the beginning of the packet. Thus, traffic seen on the air will appear as shown in Figure 5-1.

FIGURE 5-1: PACKET FORMAT

# 5.2.1 PREAMBLE/START-OF-FRAME DELIMITER

When transmitting and receiving data with the MRF24J40, the preamble and Start-of-Frame delimiter bytes will automatically be generated or stripped from the packets when they are transmitted or received. The host controller does not need to concern itself with them. Normally, the host controller will also not need to concern itself with the CRC, which the MRF24J40 will also be able to automatically generate when transmitting and verify when receiving. The CRC fields will, however, be written into the receive buffer when packets arrive, so they may be evaluated by the host controller if needed.

#### 5.2.2 LENGTH

The length field is a 1-byte field which defines the size of the packet excluding itself, the preamble and SFD, but including all other bytes of the packet, including FCS.

#### 5.2.3 FRAME CONTROL

The frame control field describes the format of this packet. It defines the type of packet (beacon, data, ACK, etc.) the addressing modes used, if the packet is encrypted or not, if the packet requires an ACK and if the packet is an intra-PAN network. This information is used by the host controller to determine how to decipher the data that follows the frame control field.

#### 5.2.4 SEQUENCE NUMBER

The sequence number field is a 1-byte sequence number that distinguishes packets. The sequence number field is used in the Acknowledgement process. An ACK packet contains no addressing information, so the uniqueness of the sequence number is the sole determining factor for verifying that a packet reached its destination. The MRF24J40 has an Auto-Acknowledgement feature that is described in **Section 7.1** "Transmitting Packets".

# 5.2.5 DESTINATION ADDRESS INFORMATION

The destination address fields of an IEEE 802.15.4 packet can change depending on the frame control field of that packet. The frame control field can specify that no destination address is present, or can specify that the short address (2 bytes) or long address (8 bytes) is present. In all cases where an address is specified, the destination PAN identifier will also be included. On incoming packets, the MRF24J40 will filter out packets that do not match the preconfigured addressing information for that radio. This eliminates any software intervention for packets that do not meet the addressing requirements. When transmitting the host controller is required to write the appropriate destination address into the transmit buffer.

#### 5.2.6 SOURCE ADDRESS INFORMATION

The source address fields of an IEEE 802.15.4 packet can change depending on the frame control field of that packet. The frame control field can specify that no destination address is present, or can specify that the short address (2 bytes) or long address (8 bytes) is present. The frame control can also specify, by using the intra-PAN bit, that the source PAN matches the destination PAN and is thus, not included in the packet.

Long addresses consist of two portions. The first three bytes are known as the Extended Organizationally Unique Identifier (EUI). EUIs are distributed by the IEEE 802.15.4. The last five bytes are address bytes which can contain the needed requirements at the discretion of the company that purchased the EUI.

When transmitting packets, the assigned source long or short address, depending on the setting of the frame control field, must be written into the transmit buffer by the host controller. The MRF24J40 will not automatically include the source address information.

#### 5.2.7 DATA

The data section of the packet can vary in length from 0 bytes to 122 bytes. Packets that exceed 127 bytes, including the frame control, source addressing, destination addressing, data and FCS fields, will be filtered out by the MRF24J40.

#### 5.2.8 FCS

The FCS field is a 2-byte field which contains an industry standard, 16-bit CRC calculated with the data from the frame control, sequence number, destination, source, and data fields. When receiving packets, the MRF24J40 will check the CRC of each incoming packet. If the RXCRCEN bit (RXMCR<1>) is cleared, packets with invalid CRCs will automatically be discarded. If RXCRCEN is set, and the packet meets all other receive filtering criteria, the packet will be written into the receive buffer and the host controller will be able to determine if the CRC was valid by reading the receive status vector (see Section 7.3 "Receiving Packets").

When transmitting packets, the MRF24J40 will automatically generate a valid CRC and transmit it attached to the end of the packet if the TXCRCEN bit (RXMCR<7>) is cleared.

### 6.0 INITIALIZATION

#### 6.1 Overview

Legend:

R = Readable bit

-n = Value at POR

Before the MRF24J40 can be used to transmit and receive packets, certain device settings must be initialized. Depending on the application, some configuration options may need to be changed. Normally, these tasks may be accomplished once after Reset and do not need to be changed thereafter.

### 6.2 Receive Filters

U = Unimplemented bit, read as '0'

'0' = Bit is cleared

To minimize the processing requirements of the host controller, the MRF24J40 incorporates several different receive filters which can automatically reject packets which are not needed. These options are controlled through the RXMCR register.

x = Bit is unknown

REGISTER 6-1: RXMCR: RECEIVE FILTER CONTROL REGISTER

W = Writable bit

'1' = Bit is set

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0   | R/W-0 |

|---------|-------|-------|-------|----------|-------|---------|-------|

| TXCRCEN | r     | ACKEN | r     | PANCOORD | COORD | RXCRCEN | PROMI |

| bit 7   |       |       |       |          |       |         | bit 0 |

| bit 7 | TXCRCEN: No CRC Data with Normal FIFO bit                                                                            |

|-------|----------------------------------------------------------------------------------------------------------------------|

|       | 1 = CRC is disabled for the TX FIFO                                                                                  |

|       | 0 = CRC is enabled for the TX FIFO                                                                                   |

| bit 6 | Reserved: Maintain as '0'                                                                                            |

| bit 5 | ACKEN: No ACK Respond in Any Case bit                                                                                |

|       | 1 = ACK response is always disabled                                                                                  |

|       | 0 = ACK response enabled. ACKs are returned when they are requested.                                                 |

| bit 4 | Reserved: Maintain as '0'                                                                                            |

| bit 3 | PANCOORD: PAN Coordinator bit                                                                                        |

|       | 1 = Set as PAN coordinator                                                                                           |

|       | 0 = Not set as PAN coordinator                                                                                       |

| bit 2 | COORD: Coordinator bit                                                                                               |

|       | 1 = Set as coordinator                                                                                               |

|       | 0 = Not set as coordinator                                                                                           |

| bit 1 | RXCRCEN: Error Report bit                                                                                            |

|       | 1 = RX all kinds of PKT (including CRC error)                                                                        |

|       | 0 = Only RX PKT (CRC ok)                                                                                             |

| bit 0 | PROMI: RX All Kinds of PKT bit (CRC ok)                                                                              |

|       | 1 = RX all kinds of PKT (CRC ok)                                                                                     |

|       | 0 = Discard PKT when there is a MAC address mismatch, illegal frame type, dPAN/sPAN or<br>MAC short address mismatch |

|       | mile chert address mismatori                                                                                         |

#### 6.3 PHY Initialization

The physical layer of the MRF24J40 controls the current levels going to different sections of the device, as well as thresholds and controls used in packet reception and transmission. There are several registers that may require modification in order to operate in the application's intended mode.

Note: The RSSI threshold defaults to '0', however, it can be set to a user-defined RSSI threshold limit. Please note, any RSSI value resulting from a CCA request that is below the RSSI threshold limit will result in a failure.

#### REGISTER 6-2: RFCTRL2: RF CONTROL REGISTER 2

| R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0   |

|----------------------|-------|-------|-------|-------|-----|-----|-------|

| RFPLL <sup>(1)</sup> | r     | r     | r     | r     | _   | -   | _     |

| bit 7                |       |       |       |       |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 **RFPLL:** RF-PLL Control bit<sup>(1)</sup>

1 = PLL enabled 0 = PLL disabled

bit 6-3 **Reserved:** Maintain as '0' bit 2-0 **Unimplemented:** Read as '0'

**Note 1:** PLL must be enabled for RF reception or transmission.

#### REGISTER 6-3: RFCTRL3: RF CONTROL REGISTER 3

| R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | U-0 | U-0 | U-0   |

|-------|-------|-------------|-------|-------|-----|-----|-------|

|       | TX    | (POWER<7:3> |       |       | _   | _   | _     |

| bit 7 |       |             |       |       |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-3 TXPOWER7:TXPOWER3: Small Scale Control for TX Power in dB bits

00000 = 0 dB

00001 = -1.25 dB

00010 = -2.5 dB

00011 = -3.75 dB

$0.0100 = -5 \, dB$

00100 = -5 dB

00101 = -6.25 dB

00110 = -7.5 dB00111 = -8.75 dB

. . .

11111 = -38.75 dB

bit 2-0 Unimplemented: Read as '0'

#### REGISTER 6-4: RFCTRL6: RF CONTROL REGISTER 6

| R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0    | U-0 | U-0 | U-0   |

|-------|-----|-------|-------|----------|-----|-----|-------|

| TXFIL | _   | r     | r     | BATMONEN | _   | _   | _     |

| bit 7 |     |       |       |          |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 **TXFIL:** TX Filter Control bit

Recommended value: '1'.

bit 6 **Unimplemented:** Read as '0' bit 5-4 **Reserved:** Maintain as '0'

bit 3 BATMONEN: Battery Monitor Enable bit

1 = Enabled0 = Disabled

bit 2-0 **Unimplemented:** Read as '0'

#### REGISTER 6-5: RFCTRL8: RF CONTROL REGISTER 8

| U-0   | U-0 | U-0 | R/W-0  | U-0 | U-0 | U-0 | R/W-0     |

|-------|-----|-----|--------|-----|-----|-----|-----------|

| _     | _   | _   | RF_VCO | _   | _   | _   | SLPCLKOUT |

| bit 7 |     |     |        |     |     |     | bit 0     |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-5 **Unimplemented:** Read as '0' bit 4 **RF\_VCO:** VCO Control bit

1 = Enhanced VCO (recommended)

0 = Normal VCO

bit 3-1 Unimplemented: Read as '0'

bit 0 SLPCLKOUT: 20 MHz Reference Output Clock Source bit

1 = Stabilize CLKOUT while recovering from Sleep0 = Stabilize CLKOUT after a wake from Sleep

#### REGISTER 6-6: RSSITHCCA: RSSI THRESHOLD FOR CCA REGISTER

| R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----------|-------|-------|-------|-------|

|       |       |       | HRES<7:0> |       |       |       |       |

| bit 7 |       |       |           |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 RSSITHRES7:RSSITHRES0: RSSI Threshold for CCA/ED Mode bits

#### 6.4 MAC Initialization

The medium access control layer of the MRF24J40 consists of several registers that define how this device operates on an IEEE 802.15.4 network.

#### 6.4.1 DEVICE CONFIGURATION

The RXMCR, described in **Section 6.2 "Receive Filters"**, should be set to the appropriate value for the intended device operation. If the device is operating as a PAN coordinator, the PANCOORD bit should be set. If the device is operating as a coordinator, then the COORD bit should be set.

#### 6.4.2 CHANNEL SELECTION

The operational channel is selected using the RFCTRL0 register.

## REGISTER 6-7: RFCTRL0: RF CONTROL REGISTER 0

| R/W-0 | R/W-0  | R/W-0  | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|--------|--------|-------|-----|-----|-----|-------|

|       | CHANNE | L<7:4> |       | _   | _   | _   | _     |

| bit 7 |        |        |       |     |     |     | bit 0 |

### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 7-4 CHANNEL7:CHANNEL4: Channel Number bits

00000 = Channel 11

00001 = Channel 12

00010 = Channel 13

...

11111 = Channel 26

bit 3-0 **Unimplemented:** Read as '0'

#### REGISTER 6-8: RFCTL: RF MODE CONTROL REGISTER

| W-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| r     | _   | -   | r     | r     | RFRST | r     | r     |

| bit 7 |     |     |       |       |       |       | bit 0 |

### Legend:

bit 2

$R = Readable \ bit \ W = Writable \ bit \ U = Unimplemented \ bit, read as '0'$

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 Reserved: Maintain as '0'

bit 6-5 Unimplemented: Read as '0'

bit 4-3 Reserved: Maintain as '0'

RFRST: RF Reset bit

1 = Reset RF (turn off RF)0 = Normal operation

bit 1-0 Reserved: Maintain as '0'

#### REGISTER 6-9: BBREG2: BASEBAND CCA/RSSI MODE REGISTER 2

| R/W-0  | R/W-0                   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0   |

|--------|-------------------------|-------|-------|-------|-------|-----|-------|

| CCAMOI | MODE<7:6> CCATHRES<5:2> |       |       | _     | _     |     |       |

| bit 7  |                         |       |       |       |       |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-6 CCAMODE7:CCAMODE6: CCA Mode bits

00 = Reserved

01 = CCA Mode 1, carrier sense only

10 = CCA Mode 2, energy above threshold

11 = CCA Mode 3, carrier sense with energy above threshold

bit 5-2 CCATHRES5:CCATHRES2: CCA Carrier Sense Threshold bits

CCA/CS value set to 0xE or '1110'.

bit 1-0 **Unimplemented:** Read as '0'

#### REGISTER 6-10: BBREG6: BASEBAND RSSI MODE REGISTER 6

| R/W-0   | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R-1     |

|---------|--------|-------|-------|-------|-------|-------|---------|

| RSSIREQ | RXRSSI | r     | r     | r     | r     | r     | RSSIRDY |

| bit 7   |        |       |       |       |       |       | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 RSSIREQ: RSSI Mode 1 bit

1 = Initiate an RSSI calculation (write back to '0' when complete)

0 = Otherwise

bit 6 RXRSSI: RSSI Mode 2 bit

1 = Calculating RSSI for RX packet0 = No calculating RSSI for RX packet

bit 5-1 Reserved: Maintain as '0'

bit 0 RSSIRDY: RSSI Ready Signal Firmware Request bit

1 = RSSI value ready

0 = Otherwise

#### 6.4.3 LONG ADDRESSES

Every device in the world has a unique long address. Long addresses are described in more detail in Section 5.2.5 "Destination Address Information" and Section 5.2.6 "Source Address Information". EADR0-EADR7 are eight short RAM address registers in the MRF24J40 that are used to define the device's long address. These addresses should be loaded into the device during the device configuration. The MRF24J40 will automatically filter out any long address packets that do not match the contents of EADR0-EADR7.

#### 6.4.4 SHORT ADDRESS AND PAN ID

The device's short address and PAN ID are programmed into the MRF24J40 through the SADRL, SADRH, PANIDL and PANIDH registers. These registers are

located in the short RAM address space. The MRF24J40 automatically filters out packets that are specified as short address destinations with addresses that do not match these registers. The exception to this rule is packets with the broadcast short address (FFFFh) and/or the broadcast PAN ID (FFFFh). Packets that match the short address and have the broadcast PAN ID will be accepted, as well as packets with the broadcast short address that match the PAN ID. A true broadcast packet will have both the short address and PAN ID set to the broadcast address. The MRF24J40 will also receive these packets no matter what the setting of the short address and PAN ID registers.

Example 6-1 shows how to initialize the MRF24J40.

## REGISTER 6-11: PANIDL: MAC PAN LOW BYTE REGISTER

| R/W-0 | R/W-0                        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|-------|------------------------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

|       | MAC PAN Low Byte (PANL<7:0>) |       |       |       |       |       |       |  |  |  |  |

| bit 7 |                              |       |       |       |       |       |       |  |  |  |  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 PANL7:PANL0: Lower Byte of PAN Address bits

### REGISTER 6-12: PANIDH: MAC PAN HIGH BYTE REGISTER

| R/W-0 | R/W-0                          | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------|--------------------------------|-------|-------|-------|-------|-------|-------|--|--|--|

|       | MAC PAN High Byte (PANH<15:8>) |       |       |       |       |       |       |  |  |  |

| bit 7 |                                |       |       |       |       |       |       |  |  |  |

Legend:

$R = Readable \ bit \ W = Writable \ bit \ U = Unimplemented \ bit, read as '0'$

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 PANH15:PANH8: Higher Byte of PAN Address bits

### REGISTER 6-13: SADRL: MAC SHORT ADDRESS LOW BYTE REGISTER

| R/W-0 | R/W-0                                    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------|------------------------------------------|-------|-------|-------|-------|-------|-------|--|--|--|

|       | MAC Short Address Low Byte (SADDRL<7:0>) |       |       |       |       |       |       |  |  |  |

| bit 7 |                                          |       |       |       |       |       |       |  |  |  |

Legend:W = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 7-0 SADDRL7:SADDRL0: Lower Byte of Short Address bits

#### REGISTER 6-14: SADRH: MAC SHORT ADDRESS HIGH BYTE REGISTER

| R/W-0                                      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| MAC Short Address High Byte (SADDRH<15:8>) |       |       |       |       |       |       |       |

| bit 7                                      |       |       |       |       |       |       | bit 0 |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 7-0 SADDRH15:SADDRH8: Higher Byte of Short Address bits

#### **EXAMPLE 6-1: INITIALIZING THE MRF24J40**

```

void MRF24J40Init(void)

BYTE i;

WORD i:

/\star place the device in hardware reset \star/

RESETn = 0;

for(j=0;j<(WORD)300;j++){}

/* remove the device from hardware reset */

RESETn = 1;

for(j=0;j<(WORD)300;j++){}

/* reset the RF module */

SetShortRAMAddr(RFCTL,0x04);

/* remove the RF module from reset */

SetShortRAMAddr(RFCTL,0x00);

/* flush the RX fifo */

SetShortRAMAddr(WRITE_RXFLUSH,0x01);

/\star Program the short MAC Address, 0xffff \star/

SetShortRAMAddr(SADRL, 0xFF):

SetShortRAMAddr(SADRH,0xFF);

SetShortRAMAddr(PANIDL,0xFF);

SetShortRAMAddr(PANIDH, 0xFF);

/* Program Long MAC Address*/

for(i=0;i<(BYTE)8;i++)

SetShortRAMAddr(EADR0+i*2,myLongAddress[i]);

/* enable the RF-PLL */

SetLongRAMAddr(RFCTRL2,0x80);

/* set TX for max output power */

SetLongRAMAddr(RFCTRL3,0x00);

/* enabled TX filter control */

SetLongRAMAddr(RFCTRL6,0x80);

SetLongRAMAddr(RFCTRL8,0b00010000);

/* Program CCA mode using RSSI */

SetShortRAMAddr(BBREG2,0x78);

/* Enable the packet RSSI */

SetShortRAMAddr(BBREG6,0x40);

/* Program CCA, RSSI threshold values */

SetShortRAMAddr(RSSITHCCA,0x00);

SetLongRAMAddr(RFCTRL0,0x00); //channel 11

{\tt SetShortRAMAddr(RFCTL,0x04);} \hspace{0.2in} //{\tt reset} \hspace{0.2in} {\tt the} \hspace{0.2in} {\tt RF} \hspace{0.2in} {\tt module} \hspace{0.2in} {\tt with} \hspace{0.2in} {\tt new} \hspace{0.2in} {\tt setLings} \hspace{0.2in} {\tt reset} \hspace{0.2in} {\tt the} \hspace{0.2in} {\tt RF} \hspace{0.2in} {\tt module} \hspace{0.2in} {\tt with} \hspace{0.2in} {\tt new} \hspace{0.2in} {\tt setLings} \hspace{0.2in} {\tt resetLings} \hspace{0.2in} {\tt resetLings}

SetShortRAMAddr(RFCTL,0x00);

```

# 7.0 TRANSMITTING AND RECEIVING PACKETS

## 7.1 Transmitting Packets

The MAC inside the MRF24J40 will automatically generate the preamble and Start-of-Frame delimiter fields when transmitting. Additionally, the MAC can generate any padding (if needed), and the CRC, if configured to do so. The host controller must generate and write all other frame fields into the buffer memory for transmission. Before transmitting packets, the MAC registers, which alter the transmission characteristics, should be initialized as documented in **Section 6.0** "Initialization".

#### 7.2 TX FIFO Format

The TX MAC performs three major tasks conforming to IEEE 802.15.4:

- TX FIFO Control

- · Automatic CSMA-CA and Timing Alignments

- · Hardware Superframe Handling

For TX FIFO control function, TX MAC controls 4 FIFOs, including beacon, normal and 2 GTS FIFOs. When each FIFO is triggered, TX MAC performs a CSMA-CA algorithm, sends a packet to the Transmit Baseband (TXBB) at the right time, handles the retransmission if an ACK is required but not received and generates FCS bytes automatically.

The automatic CSMA-CA algorithm performs timing alignments, such as LIFS, SIFS and ACK turnaround time. The user can simply program parameters for the CSMA-CA algorithm. The TX MAC will perform automatically according these parameters.

For hardware superframe handling, TX MAC builds up the timing frame of a superframe. It includes CAP, CFP, INACTIVE and each time slot. TX MAC sends beacon, normal and GTS FIFOs at the right time, automatically, at each transmission. This largely reduces the complexity of the Beacon Enable mode of IEEE 802.15.4.

FIGURE 7-1: TRANSMIT PACKET LAYOUT

| Address         | Memory                   | Description                                                                                            |

|-----------------|--------------------------|--------------------------------------------------------------------------------------------------------|

| 0x000           | Header Length            | Length of the header. This field is described in more detail in the security section of this document. |

| 0x001           | Packet Length<br>(m + 3) | The length of the packet, not including the length or FCS.                                             |

| 0x002-0x003     | Frame Control            | The frame control field describing how this packet should behave.                                      |

| 0x004           | Sequence Number          | The sequence number distinguishing this packet.                                                        |

| 0x005           | Data[0]                  |                                                                                                        |

|                 | Data[]                   | The destination and source addressing information, as well as any application data.                    |

| 0x005 + (m - 1) | Data[m - 1]              | J                                                                                                      |

| 0x006 + m       | FCS[0]                   | The CRC value for the packet; written by hardware.                                                     |

| 0x007 + m       | FCS[1]                   | The chievalue for the packet, whiteh by hardware.                                                      |

|                 |                          |                                                                                                        |

#### 7.2.1 TRIGGER PACKET TRANSMISSION

The MRF24J40 handles the Clear Channel Assessment (CCA) and Carrier Sense Multiple Access Collision Avoidance (CSMA-CA) algorithms in hardware. The MRF24J40 also handles automatic retransmission of packets that require an ACK. If the frame control field

of the packet requires an ACK, the ACKREQ bit (TXNMTRIG<2>) needs to be set before transmission. Once the TX FIFO is loaded with the data to transmit the TXRTS bit (TXNMTRIG<0>) is used to transmit the packet.

### REGISTER 7-1: TXNMTRIG: TRIGGER AND SETTING FOR NORMAL FRAME (CAP) REGISTER

| U-0   | U-0 | U-0 | R-0     | R/W-0                   | R/W-0                 | R/W-0                | W-0   |

|-------|-----|-----|---------|-------------------------|-----------------------|----------------------|-------|

| _     | _   | -   | PENDACK | INDIRECT <sup>(1)</sup> | ACKREQ <sup>(1)</sup> | SECEN <sup>(1)</sup> | TXRTS |

| bit 7 |     |     |         |                         |                       |                      | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-5 **Unimplemented:** Read as '0'

bit 4 PENDACK: Data Pending Status in ACK bit

Status of the data pending bit in ACK from previous transmission. This bit is reset by hardware on the

next transmission.

1 = Data pending bit was set0 = Data pending bit was cleared

bit 3 **INDIRECT:** Activate Indirect Transmission bit<sup>(1)</sup>

1 = Indirect transmission enabled0 = Indirect transmission disabled

bit 2 ACKREQ: TX Packet in TXN FIFO needs ACK Response bit (1)

1 = ACK requested0 = No ACK requested

bit 1 SECEN: Secure Current TX Packet bit<sup>(1)</sup>

1 = Secure packet

0 = Send packet without securing it

bit 0 TXRTS: Trigger TX MAC to Send the Packet in TX FIFO bit

1 = Send the packet in the TX FIFO, automatically cleared by hardware

Note 1: This bit is cleared at the next triggering of TXN FIFO.

#### 7.2.2 TRANSMISSION STATUS

When a transmission completes, the TXIF flag of the ISRSTS register will become set. Once the TXIF bit is set, the status of the transmission is located in the TXSR register.

#### REGISTER 7-2: TXSR: TX MAC STATUS REGISTER

| R-0    | R-0     | R-0     | R-0 | R-0 | R-0 | R-0 | R-0   |

|--------|---------|---------|-----|-----|-----|-----|-------|

| TXRETE | RY<7:6> | CCAFAIL | r   | r   | r   | r   | r     |

| bit 7  |         |         |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-6 TXRETRY7:TXRETRY6: Retry Times bits

Defines the retry times of the most recent TXN FIFO transmission.

bit 5 CCAFAIL: Clear Channel Assessment (CCA) Status of Last Transmission bit

1 = CCA failed 0 = CCA passed

bit 4-0 Reserved: Maintain as '0'

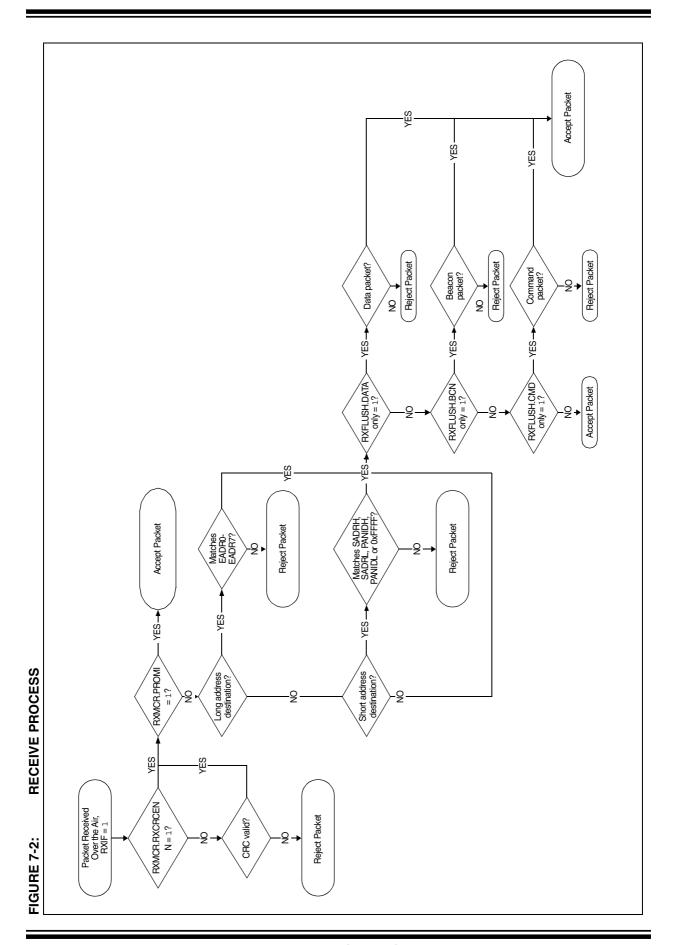

#### 7.3 Receiving Packets

The following section details the reception of a non-secured frame. When the MRF24J40 receives a packet that passes the MAC layer addressing, threshold and packet type filters, it will indicate the reception of this packet to the host controller by setting the RXIF bit (ISRSTS<3>). The packet will remain in the buffer until the host frees the buffer. No other packets can be received while the buffer is holding a packet.

#### **7.4 RX MAC**

The RX MAC block will do CRC checking, parse the received frame type and address recognition, then store the received frame into RX FIFO. In addition to the IEEE 802.15.4 packet, there are also 2 bytes of information that are appended to the end of the packet after the FCS field: LQI and RSSI.

The behavior of RX FIFO follows a certain rule. When a received packet is not filtered or dropped, a received interrupt/status will be issued. The interrupt is read-to-clear to save host operation time. However, the RX FIFO is flushed only using the following three methods:

- The host reads the first byte and the last byte to the packet

- · The host issues RX flush

- A software is reset

For RX filter function, the Promiscuous mode is supported to receive all FCS-ok packets. An Error mode is supported to receive all packets that successfully correlated PHY level preamble and delimiter.

## 7.4.1 RECEIVE PACKET LAYOUT

When a packet passes all of the enabled filters, it is placed in the receive FIFO in the following format.

FIGURE 7-3: RECEIVE PACKET LAYOUT.

| Address         | Memory                | Description                                                                          |

|-----------------|-----------------------|--------------------------------------------------------------------------------------|

| 0x300           | Packet Length (m + 5) | The length of the packet, not including the packet length, but does include the FCS. |

| 0x301-0x302     | Frame Control         | The frame control field describing how this packet should behave.                    |

| 0x303           | Sequence Number       | The sequence number distinguishing this packet.                                      |

| 0x304           | Data[0]               |                                                                                      |

|                 | Data[]                | The destination and source addressing information as well as any application data.   |

| 0x304 + (m - 1) | Data[m - 1]           |                                                                                      |

| 0x305 + m       | FCS[0]                | TI 050 1 6 11 11 11 11 11 11 11                                                      |

| 0x306 + m       | FCS[1]                | The CRC value for the packet; written by hardware.                                   |

| 0x307 + m       | LQI                   | The link quality index of the received packet.                                       |

| 0x308 + m       | RSSI                  | The received signal strength indicator for the received packet                       |

#### 7.4.2 FREEING RECEIVE BUFFER SPACE

The RX buffer is cleared when the length byte of the packet and the last byte of the FCS are read. Once both of these values are read from the RX buffer, the buffer will enable itself to receive another packet. Because the LQI and RSSI values are appended to the end of

the packet after the FCS, it may be advisable to read these values out of the RX buffer before reading the FCS.

Alternatively, it is possible to clear the RX buffer by flushing it. This is done through the RXFLUSH register.

#### REGISTER 7-3: RXFLUSH: RECEIVE FIFO FLUSH REGISTER

| U-0   | R/W-0 | R/W-0 | R/W-0    | R/W-0   | R/W-0    | R/W-0   | W-0     |

|-------|-------|-------|----------|---------|----------|---------|---------|

| _     | ŗ     | r     | RXWRTBLK | CMDONLY | DATAONLY | BCNONLY | RXFLUSH |

| bit 7 |       |       |          |         |          |         | bit 0   |

| Legend:                          |                               |                  |                        |                    |  |  |  |

|----------------------------------|-------------------------------|------------------|------------------------|--------------------|--|--|--|

| R = Reada                        | ble bit                       | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |  |  |

| -n = Value                       | at POR                        | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |  |  |

|                                  |                               |                  |                        |                    |  |  |  |

| bit 7 Unimplemented: Read as '0' |                               |                  |                        |                    |  |  |  |

| bit 6-5                          | 6-5 Reserved: Maintain as '0' |                  |                        |                    |  |  |  |

bit 6-5

Reserved: Maintain as '0'

RXWRTBLK: Software Write to RX FIFO Address bit

The solution of the solut

bit 3 CMDONLY: Command Packet Receive bit

1 = Only command packets are received, all other packets are filtered out

0 = All valid packets are received

bit 2 DATAONLY: Data Packet Receive bit

1 = Only data packets are received, all other packets are filtered out

0 = All valid packets are received

bit 1 BCNONLY: Beacon Packet Receive bit

1 = Only beacon packets are received, all other packets are filtered out

0 = All valid packets are received

bit 0 RXFLUSH: Flush RX FIFO Address bit

1 = Flush the RX FIFO. Cleared by hardware.

0 = Previous flush complete

#### 7.5 Transceiver

The MRF24J40 receiver features a low IF architecture and consists of an LNA, a pair of down conversion mixers, polyphase channel filters, baseband limiter amplifiers and RSSI technology. An ADC is used to sample the RSSI value and the sampled data is stored in a register from which the data can be read out via the SPI bus. The local oscillator generation circuits (VCO, PLL and buffers) are shared with the receiver and

transmitter. The Low Noise Amplifier (LNA) features a differential input for high performance. The RX/TX switch is integrated and LNA input and Power Amplifier (PA) output share the same pins. A common external matching network and single-ended to differential conversion is required. The transmitter features a direct conversion architecture and has a 0 to -38.75 dBm output power. The output power adjustment is in 1.25 dB step. The TX gain is programmed by the SPI bus.

#### 8.0 INTERRUPTS

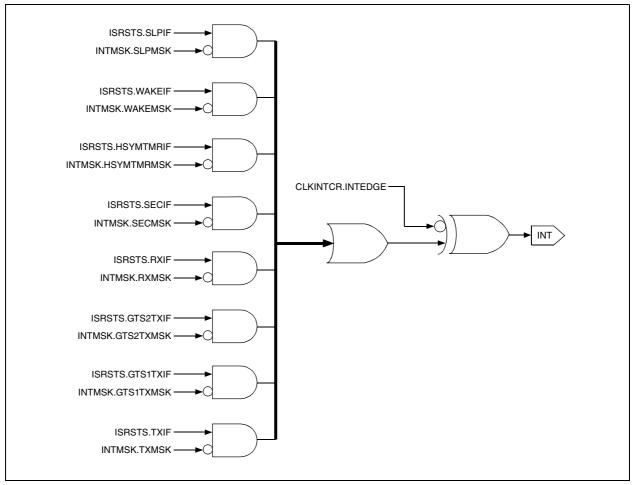

The MRF24J40 has a simple interrupt structure. There is one interrupt pin that signals all of the possible events. The ISRSTS register is a read-to-clear register that specifies which interrupt(s) caused the interrupt. The INTMSK register is used to block unwanted interrupt sources from generating interrupts. The INTEDGE bit (CLKINTCR<1>) controls the polarity of the interrupt pin. Once ISRSTS is read by the host controller, the interrupt flags are cleared. The host controller should make certain to handle all returned flags each time the ISRSTS register is read.

### 8.1 Interrupt Structure

When an enabled interrupt occurs, the interrupt pin will remain at its interrupt state, as determined by the INTEDGE bit, until all of the flags which are causing the interrupt are cleared or masked off (the mask bits are set) by the host controller. If more than one interrupt source is enabled, the host controller must poll each flag in the ISRSTS register to determine the source(s) of the interrupt.

FIGURE 8-1: MRF24J40 INTERRUPT LOGIC

# 8.1.1 INT INTERRUPT STATUS REGISTERS

The registers associated with the INT interrupts are shown in Register 8-1, Register 8-2 and Register 8-3.

### REGISTER 8-1: ISRSTS: INTERRUPT STATUS REGISTER

| RC-0  | RC-0   | RC-0      | RC-0  | RC-0 | RC-0     | RC-0     | RC-0  |

|-------|--------|-----------|-------|------|----------|----------|-------|

| SLPIF | WAKEIF | HSYMTMRIF | SECIF | RXIF | GTS2TXIF | GTS1TXIF | TXIF  |

| bit 7 |        |           |       |      |          |          | bit 0 |

| Legend:           | RC = Read to clear |                                    |                    |

|-------------------|--------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit   | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared               | x = Bit is unknown |

| bit 7 | SLPIF: Sleep Alert Interrupt bit                                                    |

|-------|-------------------------------------------------------------------------------------|

|       | <ul><li>1 = Sleep alert interrupt occurred</li><li>0 = Otherwise</li></ul>          |

| bit 6 | WAKEIF: Wake-up Alert Interrupt bit                                                 |

|       | <ul><li>1 = Wake-up interrupt occurred</li><li>0 = Otherwise</li></ul>              |

| bit 5 | HSYMTMRIF: Half Symbol Timer Interrupt bit                                          |

|       | <ul><li>1 = Half symbol timer interrupt occurred</li><li>0 = Otherwise</li></ul>    |

| bit 4 | SECIF: Security Key Request Interrupt bit                                           |

|       | <ul><li>1 = Security key request interrupt occurred</li><li>0 = Otherwise</li></ul> |

| bit 3 | RXIF: RX OK Interrupt bit                                                           |

|       | <ul><li>1 = RX OK interrupt occurred</li><li>0 = Otherwise</li></ul>                |

| bit 2 | GTS2TXIF: GTS FIFO 2 Release Interrupt bit                                          |

|       | <ul><li>1 = GTS2 transmission interrupt occurred</li><li>0 = Otherwise</li></ul>    |

| bit 1 | GTS1TXIF: GTS FIFO 1 Release Interrupt bit                                          |

|       | <ul><li>1 = GTS1 transmission interrupt occurred</li><li>0 = Otherwise</li></ul>    |

| bit 0 | TXIF: TX FIFO Release Interrupt bit                                                 |

|       | 1 = TX FIFO transmission interrupt occurred<br>0 = Otherwise                        |

#### REGISTER 8-2: INTMSK: INTERRUPT MASK REGISTER

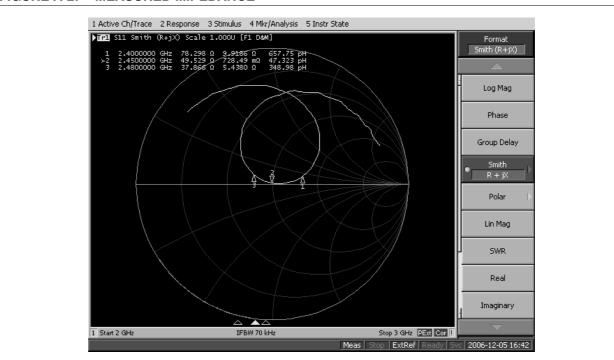

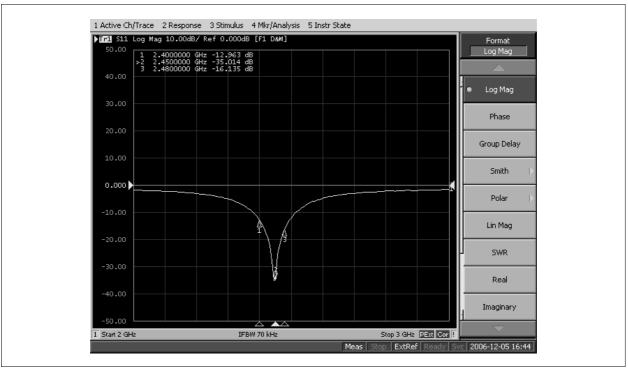

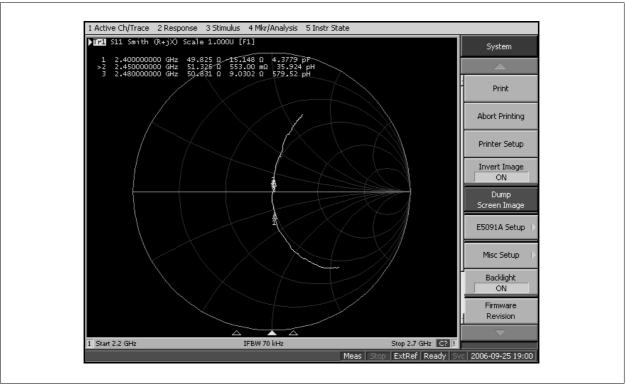

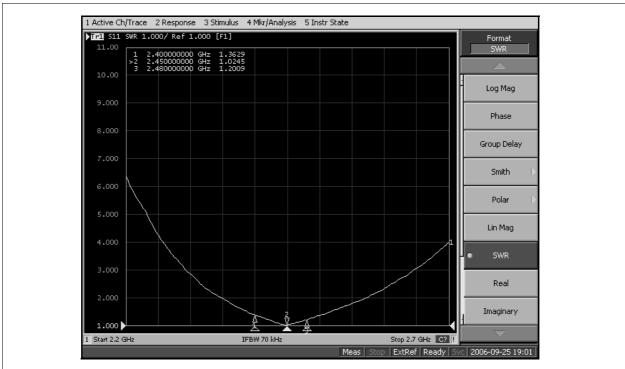

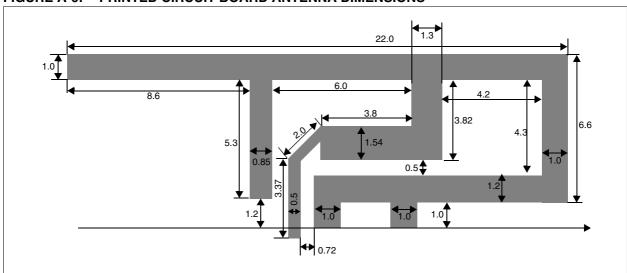

| R/W-1  | R/W-1   | R/W-1      | R/W-1  | R/W-1 | R/W-1     | R/W-1     | R/W-1 |